# POWER RECYCLE USING POSITIVE FEEDBACK ADIABATIC SYSTEM

Mrs. K. Fathima Assistant Professor, Department of Electrical and electronics Engineering, Vel Tech, Chennai, India D. Yamini Students, Department of Electrical and electronics Engineering, Vel Tech, Chennai, India

Abstract-Power consumption has become a crucial style criterion for integrated circuits. Adiabatic circuit designs consist of deliberated as well as originate with effectual at achieving minimum power on the VLSI circuit. In manuscript summarizes and suggests a novel adiabatic logic circuit depend on logic family PFAL. In the manuscript also goals to compare efficiency of established adiabatic logic circuit, based on power indulgence, and another families of adiabatic logic with bi-passing leakage energy through the capacitance based switching circuit using adiabatic ECAL logic. The recycled discrete levels of voltage are used to enable other embedded circuit that acts as common platform for all embedded modules. The comparative results are presented in various frequencies that show the lowest power dissipation of established logic circuit. PFAL contribute the better method to invert the energy store in output node capacitance rather than discharge it through ground node.

# Keywords—adiabatic, ECAL adiabatic logic, FPGA, low power, VLSI, PFAL, VLSI circuit

# I. INTRODUCTION

Nowadays Power dissipation is more important problem in compact electronic devices. This power dissipation causes the low battery backup. So, energy potency has become the main concern within transportable equipment to induce higher performance to low power dissipation. Since power indulgence at device maximizes, additional circuits are needed to cool the device as well as keep it as thermal breakdown that also outcomes at maximize whole area of device. To overwhelm these issues, the indulgence capacity of circuit must be minimized to adopt completely different low power techniques. The current manuscript focus the completely unique energy economical method known adiabatic logic that predicated in principle of energy recovery. Due to the method, rather than discharge, energy inspired is used back with capacity supply, thus minimizing on the whole power consumption. (Satoh, and Moruka 2002).

# A. Adiabatic Logic

R.Anurathi UG Students, Department of Electrical and electronics Engineering, Vel Tech, Chennai, India S.Janani UG Students, Department of Electrical and electronics Engineering, Vel Tech, Chennai, India

Adiabatic must an expression of Greek origin, which have spent majority of history associated with conventional physics. It denotes the system within a transition occurs without energy (generally heat type) become lost or obtained as system. Due to background of systems electronic, rather than heat, the electronic charge conserved. Therefore, ideal adiabatic circuit must work without loss or profit of charging electron. (Moradi et al.,2009).

Since, Second Law of Thermodynamics, it is not probable to entirely convert energy as valuable effort.

Therefore, "Adiabatic Logic" is employed though explain logic families, which might on paper work while not losses. This method "Quasi-adiabatic logic" is employed through illustrate logic, which operates at minimum power to static logic CMOS, however yet it consists of few non-adiabatic theoretical loss. Based on every case, word is used to point as systems square measure able on operation as well low power indulgence to ancient static circuits CMOS [3, 4]. (Mishra, and Singh 2014; Darwin et al., 2016).

Adiabatic circuit's square measure minimum-power circuits that employed "reversible logic" with protect energy. Adiabatic circuit's square measures that operate on the adiabatic charge as well as discharge principle and recycle energy as output nodes instead of discharge it to ground. Conventional circuits CMOS reach a logical "1" or a logical "0" by charging the load capacitor to supply voltage and discharging it to ground respectively. As such, every time a charge-discharge cycle occurs, a quantity of energy is similar with V ^ 2 C is dissipated. Nothing like traditional CMOS circuits, energy is recycled at adiabatic circuits. In addition to discharge the ground capacitance, charge is released with power supply. Since charge should be discharged to produce, the supply at adiabatic circuits denotes variable time known as power clock. Among the various waveforms to charge or discharge load capacity, it has been found that a ramp is well organized as well as, trapezoidal power clocks have utilized at various styles of adiabatic circuit [2]. Several adiabatic logic circuits that disperse minimum power to static CMOS logic

circuits are presented as talented method in low power circuit style. (Di Pascoli et al.,2014; Kumar, and Jaggil 2012; Kushawaha, and Sasamal 2015)

# **B.** Positive Feedback Adiabatic Logic

Structure of partial recovery energy circuit called adiabatic regeneration logic is employed, as displays minimum energy expenditure compare with another family at same time, as well as better strength beside scientific differentiations in the parameters.

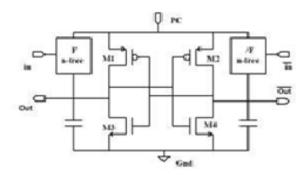

In entire core gates of PFAL denotes adiabatic electronic equipment, create latch through PMOS M1-M2 as well as NMOS M3-M4, which prevents degradation of logic level at nodes external (Shin et al.,2007) Logic functions perform two n-trees. Logical family jointly originates each positive as well as negative output.

Fig.1. Basic structure of Positive Feedback

# II. FPGA DEVELOPMENT BOARDS AND KITS

Programmable logic technologies, like field programmable gate arrays (FPGAs) is necessary component of the modern circuit design toolkit (Chow et al.,1999). Based on ability extroverted especially suitable as broad range of applications. FPGA is perfect to solve various issues in front of the rapidly developing technology sector. Based on key edges of scheduled logic technology embrace huge flexibility, value savings compared to custom semiconductors as well as hyperbolic performance through hardware correspondence.

Fig.2. FPGA hardware kit

For more than a decade, we proudly operate a Xilinx to broaden our expertise as well as facilitate the evolvement of excite novel technology. We present training as well as research platforms to our partnership to Xilinx University Platforms, enable hopeful engineers from around the world. Along, they empower the next generation of circuit designers. Field programmable gate array (FPGA) denotes microcircuit design organized to client or designer once manufactured, therefore, "field programmable". FPGA configuration is mostly nominal using a hardware description language (HDL) (Galloway 1995) almost similar, which utilized to applicationspecific microcircuit (ASIC) AN (circuit diagrams did not usually identify the configuration, they were ASICs, but maximizing rare). Contemporary FPGAs consists of great logical gate resources as well as RAM blocks to perform complex digital calculations. Because FPGA designs uses very quick I / O as well as bi-directional data buses, become challenging to validate the correct time for suitable data as setup time and timeout. The floor that comes with permissions allows resource allocation at FPGA intervals to meet these time restrictions. FPGAs are likely to perform a logical operation, which may implemented by an ASIC. The capability to upgrade functionality after dispatch, partial reconfiguration of a part of RTL generally denotes as flow of data within systems, such as dataflow among records. RTL is generally employed to combined logic style (Wibowo 2011; Cirstea,, & Dinu 2007)

# A. Block Diagram

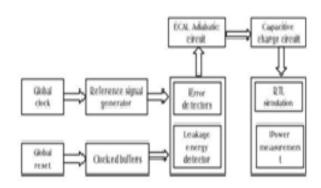

Block diagram illustrates on how the whole process takes place. Adiabatic circuits are used to bi-pass the leakage energy through capacitance based switching circuit using ECAL adiabatic logic. Basically, we set a standard or benchmark circuit which has minute loss for sure. This helps to detect those losses and recycle in capacitor and further it can be used in other embedded circuit. The energy leakage is very minute and it can be stored in a rechargeable capacitor. The recycled discrete levels of voltage are used to enable other embedded circuits.

Fig.3 Block diagram of FPGA adiabatic system model.

#### III. SOFTWARE DEALING WITH VLSI CIRCUITS

VLSI digital circuits are predominantly depending on CMOS. Based on normal blocks way, such as latches and gates, are performed as various types of students have view so far, however the behavior denotes similar. The entire miniaturization consists of novel things to examine.

Lots of thought need to be given to actual performance and design. Let's look at few factors considered.

- 1. Circuit Delays: Large, complicated circuits operating at great frequency consist of one big issue to resolve: the issues of delay at propagation signal to gates as well as cables ... even the areas of some micrometers wide! The operating speed is so great that as delays increase, they may really suit comparable with clock speeds.

- 2. Power: Another method of great operating frequency is maximized power consumption. It consists of double effect: devices use batteries quicker as well as heat indulgence maximizes. Along with fact that the surface area is reduced, the heat represents a great threat with stability of circuit itself.

- 3. Layout: The distribution of the components of the circuit is a task common to all branches of electronics. What is so special in our case is that there are. Power dissipation as well as circuit speed consists of compensation; if we try to optimize in one, another one is precious. The choice among two is demonstrated through how we select the design of circuit components. The design can also affect the manufacturing of VLSI chips, creation it simple or hard to perform the components in silicon.

### A. VLSI Basics

The earliest semiconductor chips contained two transistors each. Subsequent advancements of additional as well as additional transistors denote the significance; additional functions or individual system was included more time. Initial integrated circuits controls couple of devices, possibly to ten diodes, transistors, resistors, as well as capacitance, includes single or many logic gates manufactured at unique device. At present retrospectively recognized Small Scale Integration (SSI), performed method lead devices to hundreds of logic gates, and called Medium Scale Integration (MSI). Other methods lead Large Scale Integration (LSI), that is, systems smaller to 1,000 logic gates. Today's knowledge is gone too beyond the brand, as well as today's microprocessor consists of countless multiple gates as well as billions of particular transistors. Very Large Scale Integration (VLSI) denotes technique to create IC's to combine thousands of transistors on unique chip. Performance of circuit designers previously employed graphic schematic capture software as well as specially written as software programs of manuscript as well as simulated electronic circuits.

# **B. XILINX Software**

Yankee Technology Company, mainly seller of schedulable logic devices. As renowned to invent sector programmable gate array because initial semiconductor group

to tale model of manufacturing. Founded the a geographic region on 1984, as headquartered group of San Jose, California, to extra office at Longmont, Colorado; Dublin, Ireland; Singapore; Hyderabad, India; Beijing, China; Shanghai, China as well as Tokyo, Japan.

Xilinx designs, evolves as well as market schedulable product logic, consists of ICs, software design tools, system functions deliver IP cores, service design, client training, field engineer, as well as help technical. Xilinx sold each FPGA as well as CPLD to equipment manufacturers at finish markets like communications, industry, consumer, automotive, as well as data processing. Xilinx suggested novel large capability 3D FPGAs, consists of Virtex-7 2000T as well as Virtex-7 H580T goods, devices begin with outface capacitance of design software Xilinx's that lead company with fully revamp in set of tool. Suggested outcomes of Vivado style Suite that minimizes time required to logic programmable I/O style, as well as integration system speed and performance compared with earlier software.

#### IV. MODEL SIM

Mentor Graphics ModelSim ME alpha-lipoprotein machine could be a source-level authentication tool, allow to validating the alpha-lipoprotein code line by line. You may perform the simulation in entire levels: dynamic functions, structural as well as annotate in reverse imitation. Along to leading commercial alpha-lipoprotein scavenging ability, ModelSim is called as offering high performance, simple use, as well as excellent product support. Easy-to-use graphical programming allows to rapidly determining as well as correct problems, with the help of dynamically upgraded windows. For instance, when you choose a design region at Structure window, Source, Signals, Process, as well as Variable window is automatically upgraded. Cross-linked ModelSim windows produce an associated grade user friendly correct atmosphere. A problem is obtain you may edit, recompile, as well as re-simulate leaving-less simulator. ModelSim ME is absolutely compatible to current VHDL as well as Verilog standard language. You may imitate activity, RTL, as well as gate level code individually or at the same time. ModelSim is compatible with all small semi FPGA libraries, ensuring accurate timing simulation. Comprehensive program creates economical utilize of desktop land. Intuitive layout based on interactive graphic elements. Windows, toolbars, menus, etc. make it simple to see as well as implement modelsim denotes various powerful ability. The outcome denotes feature-rich program, which is easy to use and quickly downloads.

#### V. SIMULATION RESULT

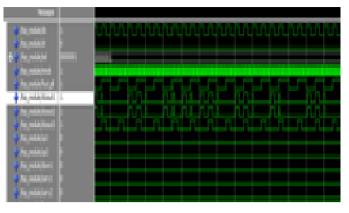

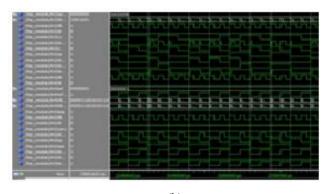

The Positive Feedback Adiabatic Logic gates are designed and simulated using modelsim Tools.

(a)

(b)

Fig.4. Logic gate analysis

#### VI. CONCLUSION

FPGA based adiabatic system ensure secure and stable operation of the power system. The performance of the planned controller is evaluated underneath completely different disturbances. It is observed that FPGA is slightly more effective than other controller. We conclude that the planned adiabatic logic circuit is beneficial for extreme minimum power applications. This paper shows the simulation results of universal gates and conjointly compares the facility values.

- Ongoing research to introduce adiabatic logic depends on carbon nanotube. If carbon annotations turn into progeny flat transistors CMOS, it suggests the remarkable impact on energy savings as well as enhanced performance, particularly at adiabatic logic. Based on superior transport, it offers a small ignition resistance and therefore exceptionally applicable at adiabatic logic, where energy per operation depends not only on capacity, as static CMOS, and resistance.

- 2. The study of the assessment of adiabatic logic associated to various types of multipliers at various parameters can also be done at future.

VII. REFERENCE

- [1] Satoh,A., and Moruka,S.(2002).An optimized s-box circuit architecture for low power aes design. In Cryptographic Hardware and Embedded System -CHES , (pp.172-186).

- [2] Moradi, A., T. M.,Shalma,M., and Salmasizadeh, M.(2009).Dual-rail transition logic: A logic style for counteracting power analysis attracks Computers & Electrical Engineering, (pp. 359-369).

- [3] Mishra,A.,and Singh, N.,(2014)Low Power Circuit Design Using Positive Feedback Adiabatic Logic (PFAL) International Journal of Science and Research (IJSR),

- [4] Darwin,S., Sheela Merlin, M.,Sindhuja,D. and . Sowmiya,M.(2016) Analysis and Design of Positive Feedback Adiabatic Logic (PFAL) Based Universal Gates.

- [5] Di Pascoli,S. and Reyneri, Vetuli, L.M;(2014)Positive Feedback in Adiabatic Logic.

- [6] Kumar, R., and Jaggil, T., (2012) Performance Analysis of Positive Feedback Adiabatic Logic for Low Power.

- [7] .Kushawaha,S.P.S., and Sasamal.T.N;(2015),Modified positive feedback adiabatic logic for ultra low power VLSI In Proc. 2015 International Conference on Computer, Communication and Control (IC4),(pp. 1-5,)

- [8] Shin, Y., Kim, T., Kim, S., Jang, S., and Kim, B. (2007, July). A low phase noise fully integrated CMOS LC VCO using a large gate length pMOS current source and bias filtering technique for 5-GHz WLAN. In 2007 International Symposium on Signals, Systems and Electronics (pp. 521-524).

- [9] Chow, P., Seo, S. O., Rose, J., Chung, K., Páez-Monzón, G., and Rahardja, I. (1999). The design of an SRAMbased field-programmable gate array. I. Architecture. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 7(2), 191-197.

- [10] Galloway, D. (1995, April). The transmogrifier C hardware description language and compiler for FPGAs. In Proceedings IEEE Symposium on FPGAs for Custom Computing Machines (pp. 136-144). IEEE

- [11] Wibowo, F. W. (2011). Interoperability of reconfiguring system on fpga using a design entry of hardware description language.

- [12] Cirstea, M. N., & Dinu, A. (2007). A VHDL holistic modeling approach and FPGA implementation of a digital sensorless induction motor control scheme. IEEE transactions on industrial electronics, 54(4), 1853-1864.